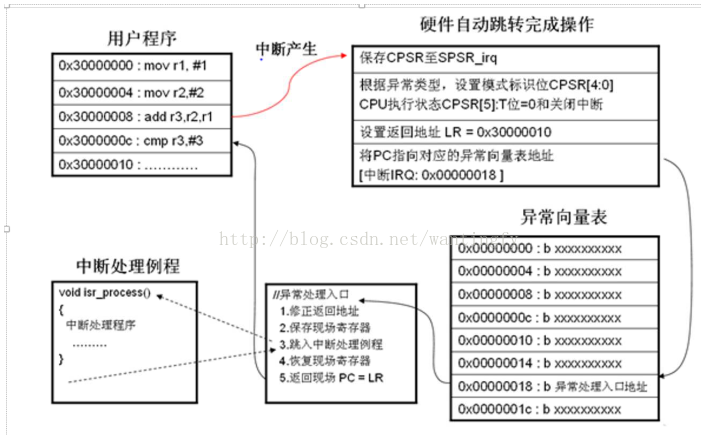

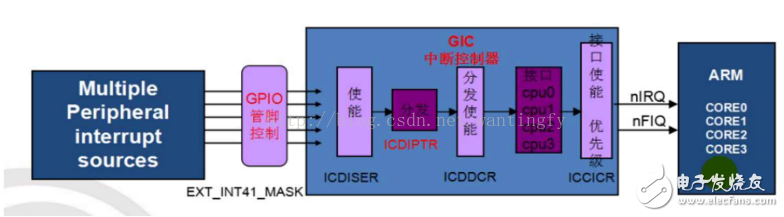

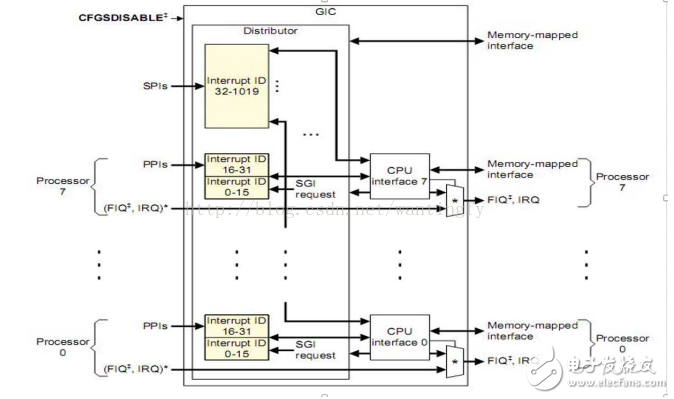

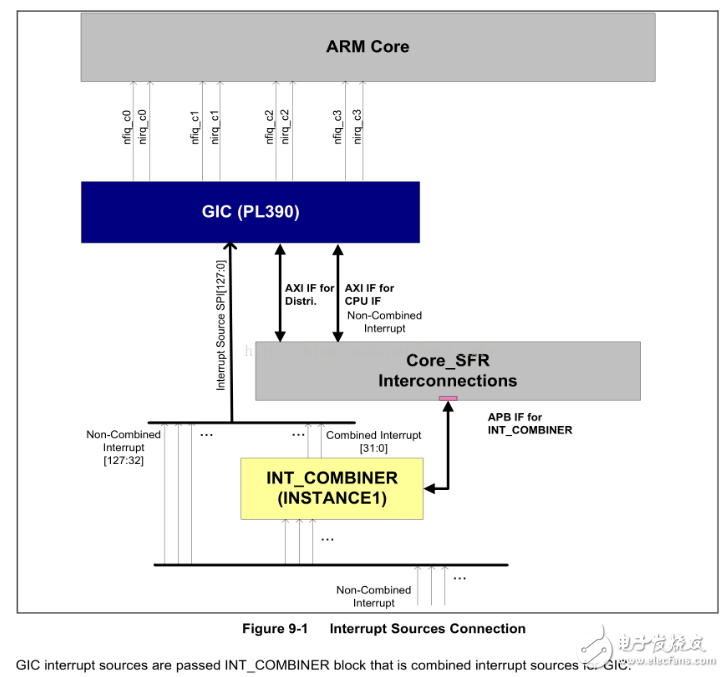

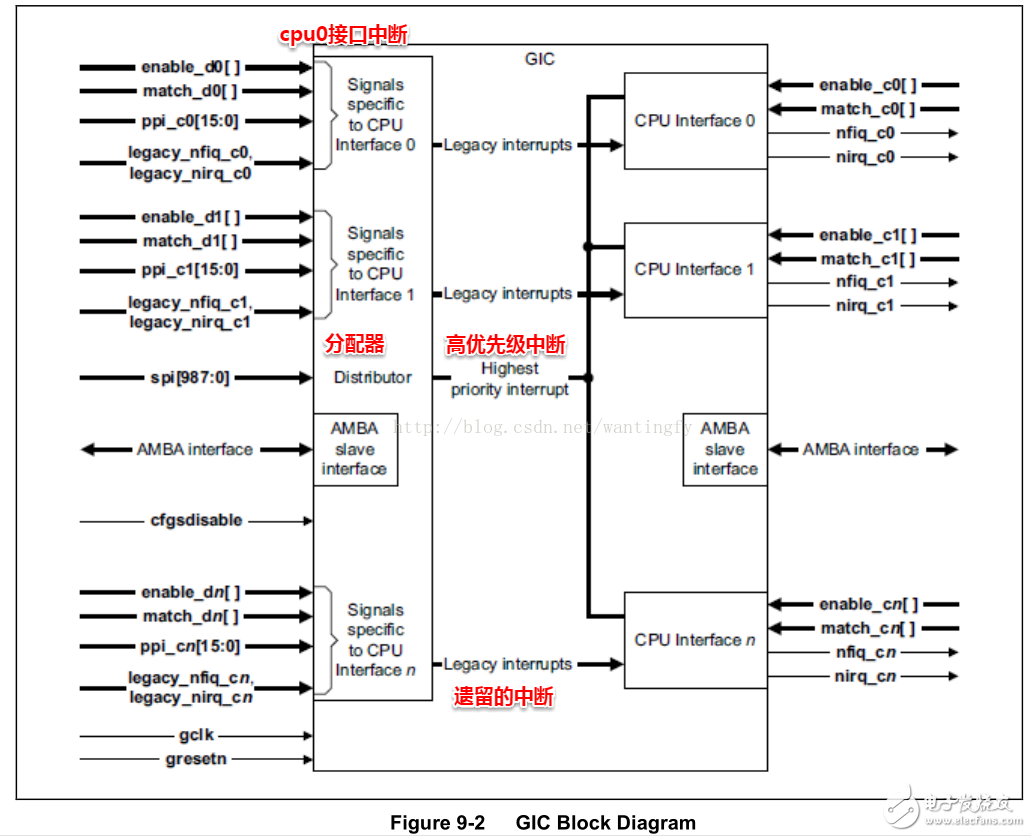

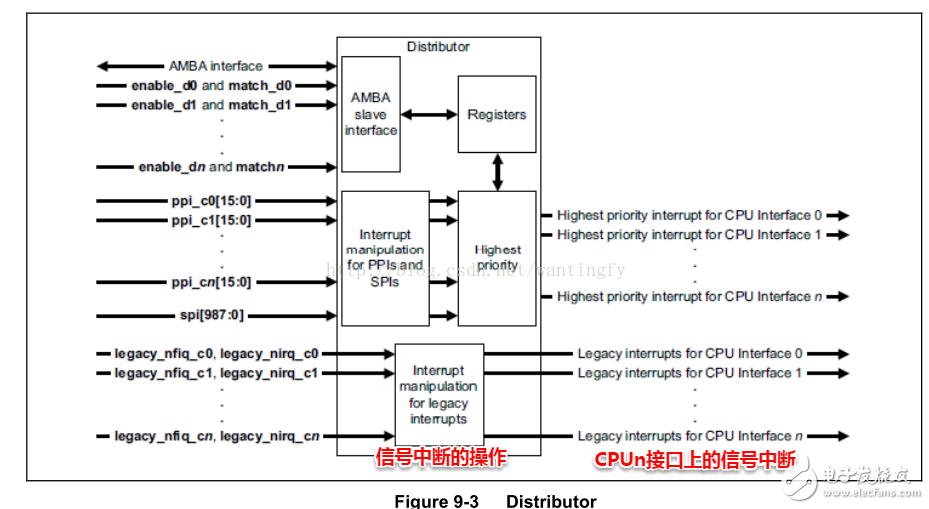

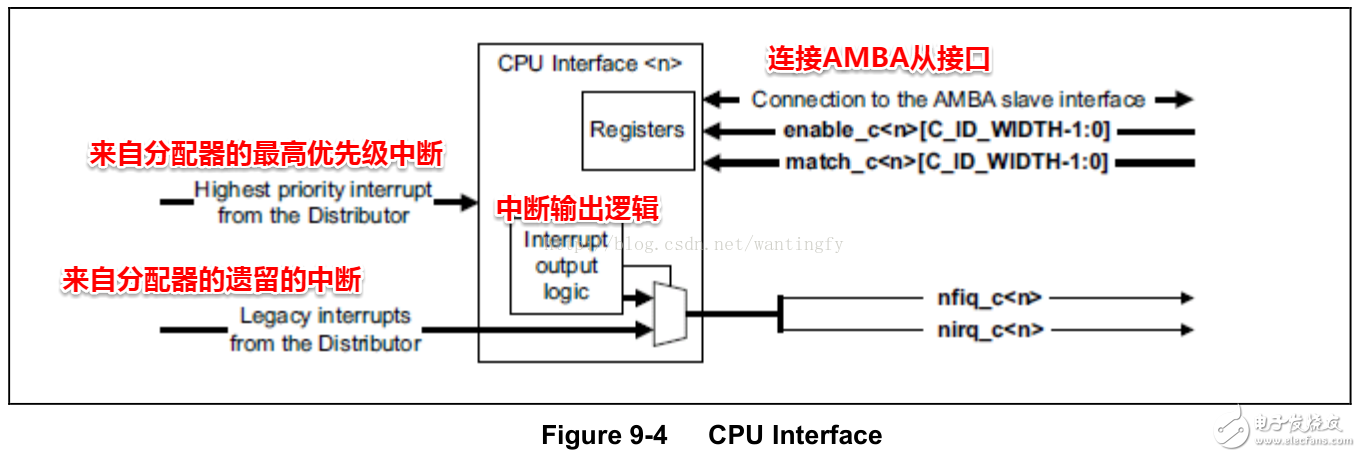

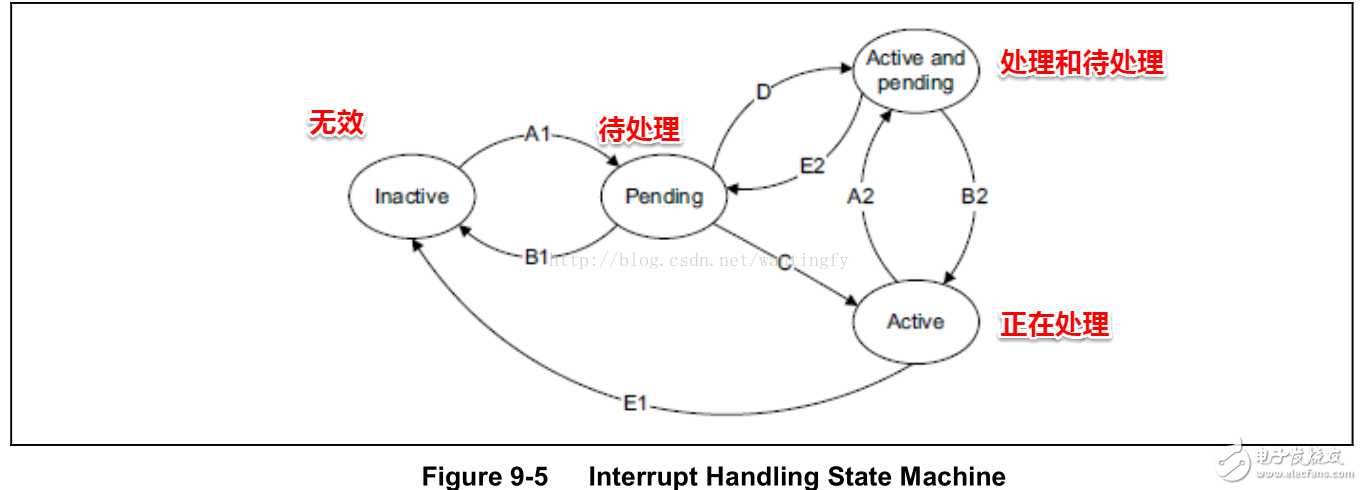

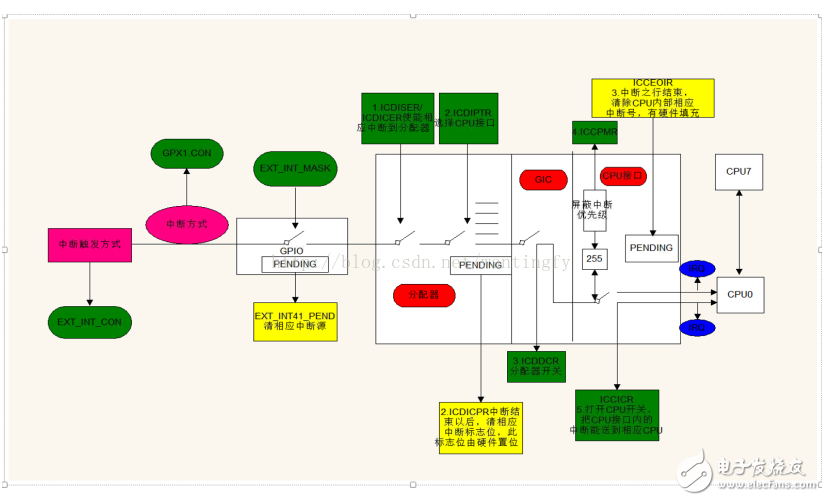

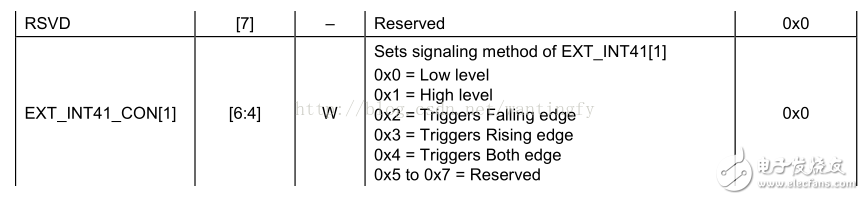

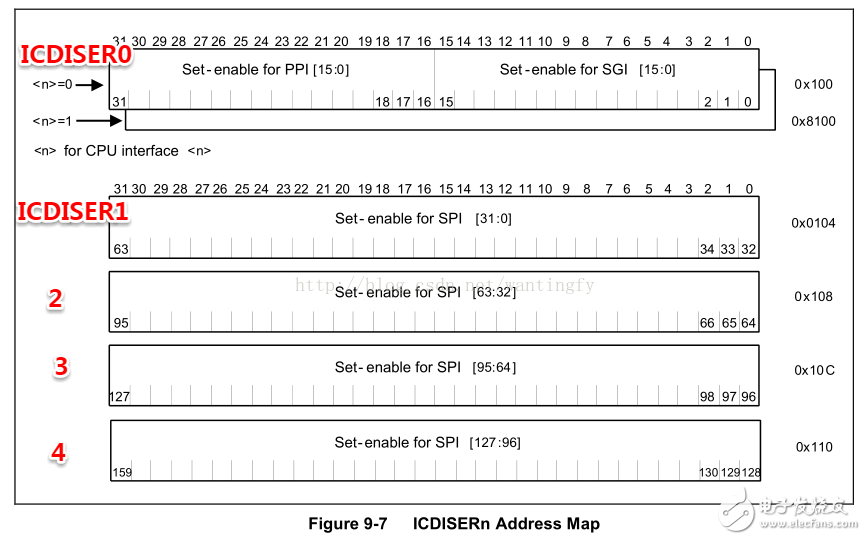

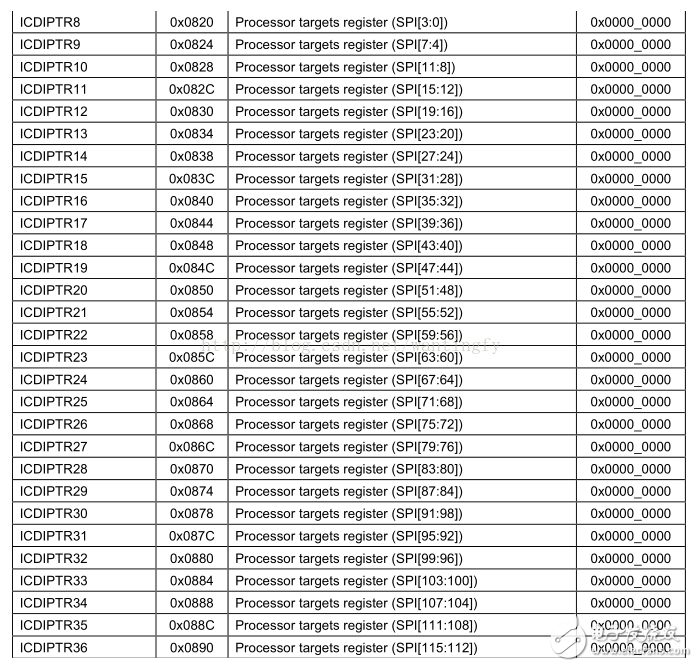

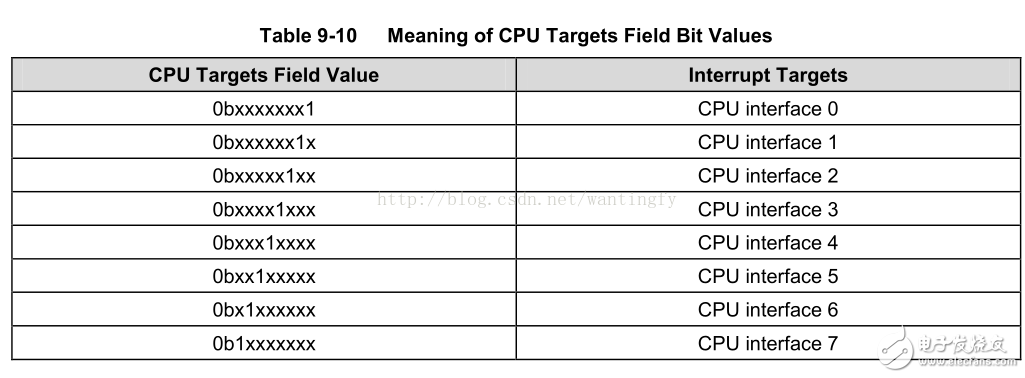

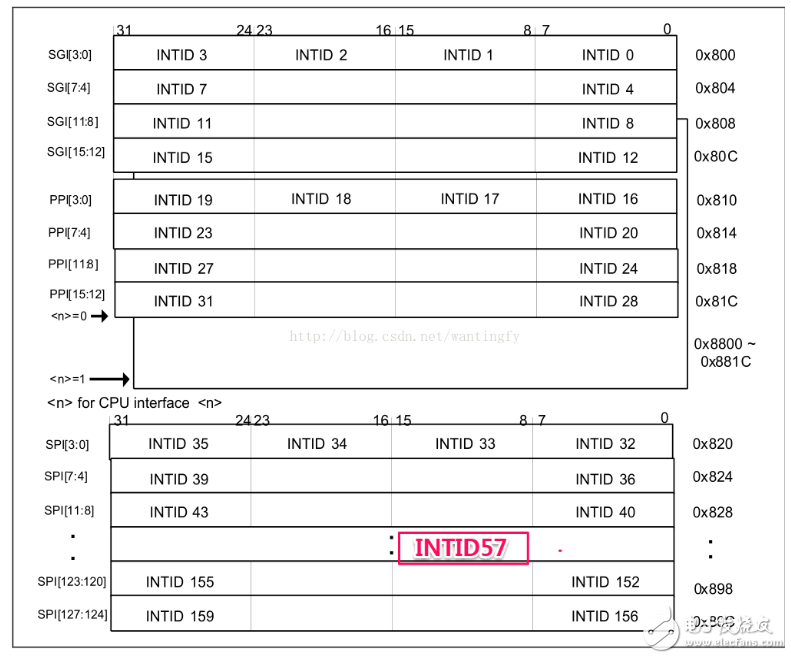

In the processor, the so-called interrupt is a process, that is, when the CPU is executing a program, it encounters external/internal emergency events that need to be processed, temporarily suspending the current program execution and turning away Serve the event. After the service is completed, return to the pause (breakpoint) to continue the original program. The program that serves the event is called an interrupt service program or interrupt handler. Strictly speaking, the above process is for hardware interrupts, and software methods can also cause interrupts. The interruption process caused by hardware is unpredictable, random, and software interruption can be controlled manually Breakpoint: An address where the program is interrupted, and instead takes the address of the execution interrupt program. Interrupt source: The signal source that caused the interrupt. The concept of exception priority When there are two interrupt sources at the same time, the problem of which interrupt to handle first appears. After this problem occurs, a concept of interrupt priority is generated here. There are 7 types of exceptions in the ARM processor. The order of priority from high to low is as follows: 1. Reset exception (reset) 2. Abnormal data (data abort) 3. Quick interrupt exception (fiq) 4. External interrupt exception (irq) 5. Prefetch exception (prefetch abort) 6. Software interrupt (swi) 7. Undefined instruction exception (undef) Hard interrupt Internal interrupt (not possible), external interrupt (can be masked), external interrupt: External interrupt generally refers to the interrupt request issued by the computer peripherals, such as: keyboard interrupt, printer interrupt, timer interrupt, etc. External interrupts are interrupts that can be masked, that is, the interrupt request of these external devices can be masked by the interrupt controller. Internal interrupt: Internal interrupt refers to the interruption caused by hardware error (such as sudden power failure, parity error, etc.) or operation error (divisor is zero, operation overflow, single-step interrupt, etc.). Internal interrupts are non-maskable interrupts. Soft interrupts (not possible), software interrupts are not really interrupts, they are just general programs that can be called and executed Interrupt response flowchart Generic interrupt control Interrupt number: Each interrupt source is assigned a unique interrupt number (0-1019) Interrupt mask: Before interrupting in assembly language, the corresponding interrupt status word needs to be authorized to allow or mask the related interrupt operation. Three types of interrupts supported by GIC Software generated interrupt SGI, software generated interrupt register (ICDSGIR). Each SGI can locate multiple processors. In the distributors and targeted processors, SGI uniquely identifies the number through the combination of its interrupts, ID0-ID15 and the processor source ID of the issuing processor (CPUID0-CPUID7) SGI. (SGI number 0-15) Interrupt numbers ID16-ID31 are used for interrupts that are private to a CPU interface and are banked in the Distributor. (PPI number 0-15) The shared peripheral interrupts the SPI, and the interrupt generated by the peripheral can be sent to one or more core processing sources. Interrupt numbers ID32-ID1019 are used for SPIs. (SPI numbers 0-987) Interrupt source GIC interrupt controller block diagram The main blocks of the GIC are: AMBA slave interface AMBA slave interface Distributor CPU interface CPU interface Clock and reset Clock and reset Enable and match signals GIC main functional modules: distributor and CPU interface The distributor receives the interrupt and provides the highest priority interrupt to the corresponding CPU interface. One Interrupts with lower priority are forwarded to the corresponding CPU interface when they become the highest priority Pending interrupt. GIC supports 160 interrupts, Total 160 interrupts including Software Generated Interrupts (SGIs [15:0], ID [15:0]), Private Peripheral Interrupts (PPIs [15:0], ID [31:16]) and Shared Peripheral Interrupts (SPIs[127:0], ID[159:32]) are supported. For SPI, you can service a maximal 32 * 4 = 128 interrupt requests (SPI number) Distributor frame diagram The Distributor provides a programming interface for: Enabling the forwarding of interrupts to the CPU interfaces globally. Enabling or disabling each interrupt. SetTIng the priority level of each interrupt. SetTIng the target processor list of each interrupt. SetTIng each peripheral interrupt to be level-sensiTIve or edge-triggered. Setting each interrupt as either secure or Non-secure if the GIC implements the Security Extensions. Sending an SGI to one or more target processors. Enable the forwarding of global interrupts to the CPU interface. Enable or disable each interrupt. Set the priority of each interrupt. Set the target processor list for each interrupt. Set each peripheral interrupt to be level sensitive or edge triggered. If the GIC performs a safe extension, each interrupt is set to be safe or unsafe. Send SGI to one or more target processors. View the status of any interruption Provide software to set or clear any interrupted suspend status Interrupts are identified by interrupt numbers, and each interface can handle up to 1020 interrupts Interrupts from sources are identified using ID numbers. Each CPU interface can see up to 1020 interrupts. The distributor supports up to 1244 interrupts because of banking of SPIs and PPIs. CPU interface Programming interface for: Enabling the signaling of interrupt requests by the CPU interface. Acknowledging an interrupt. Indicating completion of the processing of an interrupt. Setting an interrupt priority mask for the processor. Defining the preemption policy for the processor. Determining the highest priority pending interrupt for the processor. Programming interface The interrupt request signal is sent through the CPU interface. Confirm the interruption. Indicates completion of interrupt processing. Set an interrupt priority mask for the processor. Define the preemption strategy for the processor. Determine the highest pending interrupt for the processor. Interrupt state transition diagram Interrupted state inactive (inactive) Interrupt did not occur pending An interrupt occurs and waits for the core to process. The pending interrupts are all sent to the core for processing through the CPU interface. active (processing) The interrupt is given to the core, and the interrupt is currently being processed active and pending An interrupt source is being processed by the core and the GIC receives an interrupt trigger signal from the same interrupt source. Convert A1 or A2, add suspend state For SGI: Conversion occurs when writing to the ICDSGIR targeted by the specified processor. Only when the specified SGI security configuration (applicable to the CPU interface) corresponds to the ICDSGIR.SATT bit value. If GIC performs security extensions and writes ICDSGIR in Secure. For SPI or PPI, the conversion occurs if: Peripherals issue interrupt signals or The software is written to ICDISPR. Convert B1 or B2, delete pending state The transition does not apply to SGI: The pending SGI should be converted or reset through the active state to delete its suspended state. The pending SGI in the active state should be converted through the suspended state, or reset to delete the suspended state. For SPI or PPI, the conversion occurs if: Level-sensitive interrupts are only in a waiting state when the input signal is valid, asserting or triggering an edge-triggered interrupt signal, or writing an interrupt, the interrupt is in a pending state ICDISPR. The software then writes to the corresponding ICDICPR. Transition C. If the interrupt is enabled and has sufficient priority to send a signal to the processor, a software conversion occurs to read from ICCIAR. Transition D. For SGI, if the associated SGI is enabled and the distributor forwards it to the CPU interface, a conversion occurs while the processor reads ICCIAR to confirm the previous SGI instance. whether The occurrence of this transition depends on the reading time of ICCIAR and the time of SGI re-regulation. For SPI or PPI: The conversion takes place The interrupt is enabled. Read the software from ICCIAR. This read adds the activation status to the interrupt. -The interrupt signal remains active for level-sensitive interrupts. This is because peripherals do not have interrupts until the processor service is interrupted. For edge-triggered interrupts, whether or not this transition occurs depends on the timing of the ICCIAR read relative to the interrupt that detected the reinterruption. Otherwise it will cause ICCIAR to read Transition C, possibly followed by transition A2. Convert E1 or E2, delete the active state The conversion occurs when the software is written to ICCEOIR. Peripheral and interrupt controller processing flow Button status Low level (pressed state) High level (bounced state) Falling edge (the process of high-level to low-level transition) Rising edge (the process of low-level to high-level transition) Register description ICCICR_CPUn 0x0000 CPU interface control register 0x0000_0000 CPU interface control register (interrupts in the CPU interface are sent to the corresponding CPU) ICCPMR_CPUn 0x0004 Interrupt priority mask register 0x0000_0000 Interrupt priority filter register (255 all interrupts are corresponding, 0 does not correspond to any interrupt) ICDISERm_CPUn 0x0100 Interrupt set-enable register (SGI, PPI) 0x0000_FFFF Interrupt enable register (enable the corresponding interrupt to the distributor) ICDIPTRm_CPUn 0x0800 Processor targets register (SGI[3:0]) 0x0101_0101 Interrupt target CPU configuration register (select CPU interface) ICDDCR 0x0000 Distributor control register 0x0000_0000 distributor controller (open distributor) ICCIAR_CPUn 0x000C Interrupt acknowledge register 0x0000_03FF Interrupt acknowledge register ICCEOIR_CPUn 0x0010 End of interrupt register Undefined Interrupt processing end register (clear corresponding interrupt number inside CPU) ICDICPRm_CPUn 0x0280 Interrupt pending-clear register (SGI, PPI) 0x0000_0000 Interrupt status clear register (clear corresponding interrupt flag bit) Button register configuration EXT_INT41_PEND 0x0F44 External interrupt EXT_INT41 pending register 0x0000_0000 (configuration button pending pending) EXT_INT41_CON 0x0E04 External interrupt EXT_INT41 configuration register 0x0000_0000 (configuration button trigger mode) EXT_INT41_MASK 0x0F04 External interrupt EXT_INT41 mask register 0x0000_00FF (key enable interrupt) Key trigger method Specific register ICDSER selects the corresponding special management all interrupt enable register to enable interrupt according to the interrupt number ICDPTRm_CPUn, the interrupt number is 57-32=25, select ICDIPTR14 According to the GIC Interrupt Table, the EINT[9] interrupt number is 57 and the SP1 number is 57-32=25. According to the following figure, the eight-bit control CPU interface, here our CPU only has four cores, and each register controls four interrupts CPU interface selection, SPI number is 25, in SPI [27:24], here our CPU interface is 0, the value of eight bits is 0x00000001 (select which interface which interface is set to 1), so here is configured as ICDIPTR.ICDIPTR14= 0X1 《《 8 Specific case code /* * main.c * * Created on: 2017-12-4 * Author: Administrator */ #include"exynos_4412.h" voiddo_irq() { unsignedint irq_num;//Get interrupt number irq_num = CPU0.ICCIAR& 0X3FF; switch (irq_num) { case57: printf("i'm key2 interrupter! interrupter id is %d", irq_num); GPF3.DAT = 0x1 "《 4; EXT_INT41_PEND = 0X1 "< 1;//Interrupt restart ICDICPR.ICDICPR1 = 0X1 "< 25;//Clear the corresponding interrupt flag break; case58: printf("i'm key3 interrupter! interrupter id is %d", irq_num); GPF3.DAT = 0x1 "《 5; EXT_INT41_PEND = 0x1 <<《 2; // Clear the corresponding interrupt source ICDICPR.ICDICPR1 = 1 《《 26; break; default: printf ("interrupter not exist"); break; } CPU0.ICCEOIR= (CPU0.ICCEOIR& ~(0x3ff)) | irq_num;//Clear the corresponding interrupt number } voidmydelay_ms (inttime) { inti, j; while (time--) { for (i = 0; i << 5; i++) for (j = 0; j "514; j++) ; } } voidperipheral_init() { GPF3.CON= GPF3.CON& (~(0xf << 16)) | 0x1 << << 16; // lamp GPF3.CON= GPF3.CON& (~(0xf << 20)) | 0x1 << << 20; GPX1.CON = GPX1.CON& (~ (0xf "" 4)) | 0xF "< 4;//pin bit external interrupt GPX1.CON = GPX1.CON& (~ (0xf "" 8)) | 0xF "" 8; // pin bit external interrupt EXT_INT41_CON = EXT_INT41_CON & (~ (0X3 << 4)) | (0X2 << << 4);//Falling edge trigger EXT_INT41_CON = EXT_INT41_CON & (~(0X3 << 8)) | (0X2 << "8);//Falling edge trigger EXT_INT41_MASK = EXT_INT41_MASK & (~(0X1 《《 1)); //Enable interrupt EXT_INT41_MASK = EXT_INT41_MASK & (~(0X1 《《 2)); //Enable interrupt } voidgic_init() { ICDDCR =1;//Enable distributor CPU0.ICCICR = 0X1;//Enable CPU interface CPU0.ICCPMR = 0XFF;//The priority is the lowest, all interrupts will respond ICDISER.ICDISER1= (0X1 << 25> | (0x1 << 26); ICDIPTR.ICDIPTR14= (0X1 << "8) | (0x1 <<" 16); //The interrupt is sent to the corresponding CPU } intmain() { peripheral_init(); gic_init(); while (1) { printf ("working!"); GPF3.DAT= ~(0x3 《《 4); mydelay_ms (800); } };

we offer a wide selection of traffic Steel Pole structures in standard and custom designs.

Yixing Futao Metal Structural Unit Co. Ltd. is com manded of Jiangsu Futao Group.

Traffic Signal Pole,Traffic Light Pole,Led Traffic Signals,Solar Traffic Signal Pole,Traffic Steel Pole YIXING FUTAO METAL STRUCTURAL UNIT CO.,LTD( YIXING HONGSHENGYUAN ELECTRIC POWER FACILITIES CO.,LTD.) , https://www.chinasteelpole.com

What is an interrupt?

It is located in the beach of scenic and rich Taihu Yixing with good transport service.

The company is well equipped with advanced manufacturing facilities.

We own a large-sized numerical control hydraulic pressure folding machine with once folding length 16,000mm and the thickness 2-25mm.

We also equipped with a series of numerical control conveyor systems of flattening, cutting, folding and auto-welding, we could manufacture all kinds of steel poles and steel towers.

Our main products: high & medium mast lighting, road lighting, power poles, sight lamps, courtyard lamps, lawn lamps, traffic signal poles, monitor poles, microwave communication poles, etc. Our manufacturing process has been ISO9001 certified and we were honored with the title of the AAA grade certificate of goodwill"

Presently 95% of our products are far exported to Europe, America, Middle East, and Southeast Asia, and have enjoyed great reputation from our customers,

So we know the demand of different countries and different customers.

We are greatly honored to invite you to visit our factory and cheerfully look forward to cooperating with you.